Masalah konkurensi merupakan salah satu tantangan paling sulit di bidang pengembangan perangkat lunak. Ketika beberapa thread atau proses berinteraksi dengan sumber daya bersama, perilaku yang dihasilkan bisa tidak dapat diprediksi. Kondisi persaingan terjadi ketika hasil dari suatu sistem tergantung pada urutan waktu relatif dari kejadian, seperti urutan pemrosesan pesan atau cara akses data. Kesalahan logika ini sering tidak muncul selama pengujian standar, muncul hanya dalam kondisi beban atau waktu tertentu. Untuk mengatasi hal ini, insinyur membutuhkan alat yang dapat memvisualisasikan interaksi seiring waktu dan perubahan status. Diagram komunikasi menawarkan pendekatan terstruktur untuk memetakan interaksi ini.

Meng-debug logika tanpa bantuan visual seperti berkelana di kota yang rumit tanpa peta. Anda tahu tujuan Anda, tetapi jalurnya terhalang oleh persimpangan dan pola lalu lintas. Dalam konteks desain sistem, ‘lalu lintas’ terdiri dari pesan asinkron dan transisi status. Dengan menggunakan diagram komunikasi, pengembang dapat melacak aliran kontrol dan data secara eksplisit. Panduan ini menjelajahi cara memanfaatkan diagram-diagram ini untuk mengidentifikasi kondisi persaingan sebelum memengaruhi lingkungan produksi.

Memahami Kondisi Persaingan dalam Logika Sistem 🧠

Kondisi persaingan terjadi ketika dua atau lebih operasi bersaing untuk menggunakan sumber daya yang sama, dan status akhir tergantung pada urutan atau waktu eksekusi mereka. Ini bukan sekadar kesalahan pemrograman; ini adalah kelemahan logika dalam desain interaksi antar komponen. Bayangkan skenario di mana dua proses berusaha memperbarui penghitung bersama secara bersamaan. Jika siklus baca-ubah-tulis tidak bersifat atomik, satu pembaruan dapat hilang.

- Waktu-Pemeriksaan ke Waktu-Penggunaan (TOCTOU): Kerentanan klasik di mana status suatu sumber daya diperiksa pada satu titik, tetapi sumber daya tersebut digunakan pada titik berikutnya, yang berpotensi berubah di antaranya.

- Eksekusi Bersilangan: Thread mengeksekusi instruksi dalam urutan yang tidak dapat diprediksi, mengakibatkan keadaan data yang tidak konsisten.

- Penyusunan Pesan: Dalam sistem terdistribusi, pesan dapat tiba secara tidak berurutan, menyebabkan cabang logika dieksekusi berdasarkan informasi yang sudah usang.

Alat debugging tradisional sering berfokus pada tumpukan tindakan atau dump memori. Meskipun berguna, alat-alat ini tidak secara inheren menunjukkan hubungan kausal antar komponen sistem yang berbeda. Kondisi persaingan sering kali merupakan masalah hubungan, bukan hanya masalah variabel. Oleh karena itu, diagram yang menekankan hubungan dan aliran pesan lebih efektif untuk diagnosis.

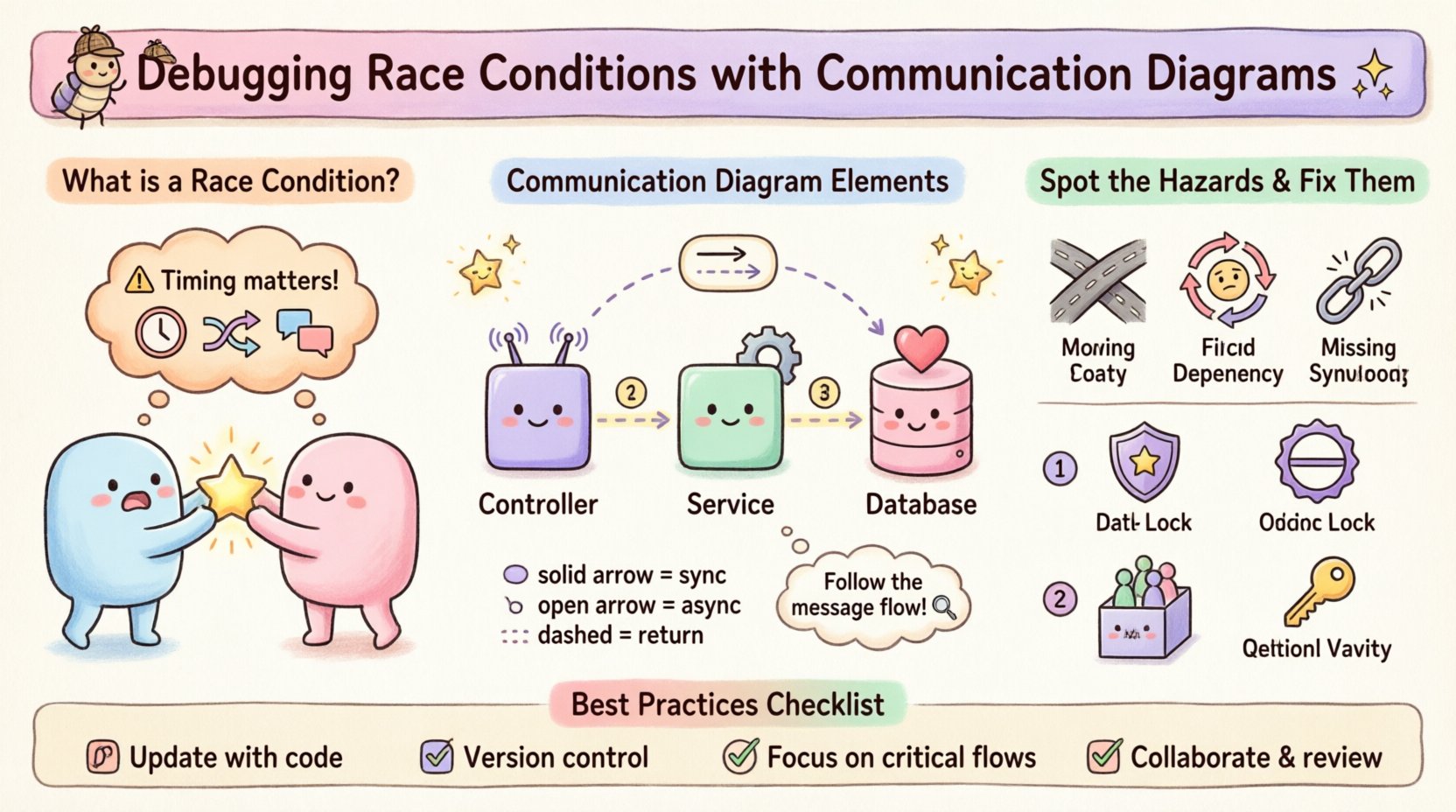

Kekuatan Diagram Komunikasi 📊

Diagram komunikasi, yang sebelumnya dikenal sebagai diagram kolaborasi dalam UML 1.x, berfokus pada organisasi struktural objek dan pesan yang dikirim antar objek. Berbeda dengan diagram urutan yang menekankan waktu secara vertikal, diagram komunikasi menekankan koneksi struktural antar objek. Perspektif ini sangat penting untuk mengidentifikasi kondisi persaingan karena menyoroti koneksi bersama.

Saat melakukan debugging, Anda mencari titik-titik di mana beberapa jalur bertemu. Dalam diagram komunikasi, titik-titik pertemuan ini sering menjadi sumber persaingan. Diagram ini terdiri dari objek, tautan, dan pesan. Setiap pesan mewakili panggilan atau sinyal. Dengan menandai pesan-pesan ini dengan batasan waktu atau tingkat prioritas, Anda dapat mensimulasikan lingkungan eksekusi.

- Objek: Mewakili entitas aktif dalam sistem, seperti Controller, Service, atau Database.

- Tautan: Menentukan jalur struktural di mana pesan bergerak antar objek.

- Pesan: Mewakili aliran logika. Mereka dapat bersifat sinkron (blok) atau asinkron (kirim dan lupakan).

Tata letak visual memungkinkan Anda melihat objek ‘pusat’ (hub). Objek-objek ini adalah yang berinteraksi dengan entitas lain paling banyak. Konektivitas tinggi sering berkorelasi dengan risiko lebih tinggi terhadap masalah konkurensi. Dengan mengisolasi pusat-pusat ini, Anda dapat fokuskan upaya debugging di tempat yang paling penting.

Menyiapkan Panggung untuk Debugging 🛠️

Sebelum menggambar diagram, Anda harus memahami cakupan masalahnya. Kondisi persaingan sering berasal dari alur kerja tertentu. Identifikasi jalur kritis di mana terjadi ketidaksesuaian data. Misalnya, jika pembaruan profil pengguna gagal secara berkala, lacak aliran dari titik akhir API ke penyimpanan data.

Berikut adalah daftar periksa untuk menyiapkan lingkungan Anda untuk analisis diagramatik:

- Tentukan Para Pihak (Actors): Daftar semua sistem eksternal atau pengguna yang memulai permintaan.

- Identifikasi Objek Internal: Pisahkan arsitektur internal menjadi komponen logis (misalnya, Cache, API, Worker).

- Daftar Pesan-Pesan:Uraikan pemanggilan fungsi atau peristiwa khusus yang terjadi selama alur kerja.

- Tandai Sumber Daya Bersama:Soroti setiap tabel basis data, variabel memori, atau kunci berkas yang diakses oleh banyak objek.

Setelah lingkup ditentukan, Anda dapat mulai membuat diagram. Tujuannya bukan membuat model arsitektur yang sempurna, tetapi sebagai artefak debugging. Sederhanakan jika diperlukan. Jika suatu komponen tidak berkontribusi terhadap kondisi persaingan, keluarkan saja. Kejelasan lebih penting daripada kelengkapan pada tahap ini.

Langkah demi Langkah: Memetakan Aliran 🔍

Membuat diagram untuk debugging memerlukan metodologi khusus. Anda sedang memetakan logika, bukan hanya struktur. Ikuti langkah-langkah berikut untuk membuat artefak debugging yang efektif.

1. Tempatkan Pemicu dan Target

Mulailah dengan menempatkan objek yang memicu permintaan di sebelah kiri atau atas. Tempatkan objek utama yang terdampak di sebelah kanan atau bawah. Ini menentukan arah aliran. Misalnya, jika sebuah UserService memanggil Database, maka objek User mengirim pesan ke Database.

2. Tambahkan Objek Perantara

Petakan setiap lapisan middleware atau penyimpanan sementara (cache). Dalam skenario kondisi persaingan, lapisan cache sering menjadi penyebab utama. Jika cache diperbarui sebelum basis data, dapat terjadi pembacaan data yang usang. Jika basis data diperbarui sebelum cache, cache dapat menampilkan data lama. Gambarlah tautan untuk setiap langkah perantara.

3. Beri Keterangan Jenis Pesan

Bedakan antara pesan sinkron dan asinkron. Pesan sinkron mengimplikasikan keadaan menunggu. Pesan asinkron mengimplikasikan perilaku ‘kirim dan lupakan’. Kondisi persaingan sering muncul dari pemanggilan asinkron di mana respons diharapkan tetapi tidak dijamin tiba dalam urutan yang benar.

- Sinkron:Gunakan garis padat dengan ujung panah padat.

- Asinkron:Gunakan garis padat dengan ujung panah terbuka.

- Pesan Balasan:Gunakan garis putus-putus dengan ujung panah terbuka.

4. Beri Label pada Tautan

Berikan nomor pada setiap pesan untuk menunjukkan urutan. Ini sangat penting untuk debugging. Dalam diagram komunikasi, urutan diimplikasikan oleh angka, bukan hanya posisi vertikal. Pastikan angka-angka tersebut mencerminkan urutan logis eksekusi sebaik mungkin menurut pemahaman Anda.

Mengidentifikasi Bahaya Konsistensi Paralel dalam Diagram ⚠️

Setelah diagram digambar, Anda harus menganalisisnya untuk pola-pola tertentu yang menunjukkan ketidakstabilan. Perhatikan tanda bahaya struktural berikut.

- Jalur yang Bertemu: Jika dua aliran pesan yang berbeda mengarah ke objek yang sama untuk mengubah data yang sama, kondisi persaingan mungkin terjadi. Ini menunjukkan adanya beberapa titik masuk ke bagian kritis.

- Ketergantungan Melingkar: Jika Objek A memanggil Objek B, dan Objek B memanggil Objek A dalam transaksi logis yang sama, sistem dapat mengalami deadlock atau berperilaku tidak terduga.

- Sinkronisasi yang Hilang: Jika pembaruan kritis dikirim secara asinkron tanpa pesan konfirmasi sebelum langkah berikutnya, logika berikutnya mungkin melanjutkan dengan data yang sudah usang.

Pertimbangkan pola ‘Double-Check Locking’. Ini adalah optimasi umum yang gagal tanpa penghalang memori yang tepat. Dalam diagram, ini tampak seperti pesan pemeriksaan diikuti oleh pesan pembaruan. Jika thread lain melakukan pemeriksaan di antara dua langkah tersebut, pembaruan akan terjadi secara tidak perlu.

Menganalisis Urutan Pesan dan Waktu ⏱️

Waktu adalah variabel tak terlihat dalam kondisi persaingan. Diagram komunikasi dapat merepresentasikan batasan waktu menggunakan catatan atau anotasi khusus. Meskipun tidak menunjukkan milidetik yang tepat, mereka menunjukkan urutan logis.

Gunakan strategi-strategi berikut untuk menganalisis waktu:

- Paralelisme:Gambar cabang-cabang paralel untuk mewakili eksekusi bersamaan. Jika dua cabang bertemu pada sumber daya bersama, urutan kedatangan menentukan hasilnya.

- Waktu Habis (Timeouts):Tambahkan anotasi yang menunjukkan waktu habis yang diharapkan. Jika pesan tidak kembali dalam waktu tertentu, apakah sistem mencoba lagi? Pengulangan dapat menyebabkan pembaruan ganda.

- Konsistensi Akhir: Jika sistem mengandalkan konsistensi akhir, diagram harus menunjukkan keterlambatan antara operasi penulisan dan ketersediaan baca. Keterlambatan ini adalah tempat di mana kondisi persaingan tersembunyi.

Sebagai contoh, jika layanan pemberitahuan mengirim email setelah pembayaran dikonfirmasi, tetapi konfirmasi pembayaran bersifat asinkron, email mungkin dikirim sebelum uang benar-benar terjamin. Diagram harus secara eksplisit menunjukkan celah antara peristiwa konfirmasi pembayaran dan pemicu email.

Pola Umum yang Menyebabkan Ketidakstabilan 🔄

Beberapa pola arsitektur rentan terhadap kondisi persaingan. Mengenali mereka dalam diagram Anda dapat mempercepat proses debugging.

| Pola | Deskripsi Risiko | Indikator Diagram |

|---|---|---|

| Baca-Sunting-Tulis | Dua proses membaca nilai yang sama, mengubahnya, dan menuliskannya kembali. Tulisan kedua menimpa yang pertama. | Banyak pesan yang mengarah ke penyimpanan data yang sama tanpa menunjukkan mekanisme kunci. |

| Kirim dan Lupakan | Suatu peristiwa dipicu tanpa menunggu konfirmasi. Logika berikutnya mengasumsikan keberhasilan. | Panah pesan asinkron tanpa jalur kembali atau pesan konfirmasi. |

| Invalidasi Cache | Data diperbarui di basis data tetapi tidak di cache, atau sebaliknya. | Jalur paralel ke Database dan Cache tanpa titik sinkronisasi. |

| Kegagalan Idempotensi | Permintaan diulang, menyebabkan tindakan ganda terjadi. | Panah loopback yang menunjukkan ulang percobaan tanpa pemeriksaan ID transaksi unik. |

Ketika Anda melihat pola-pola ini dalam diagram Anda, berhenti sebentar. Tanyakan pada diri sendiri: ‘Apa yang terjadi jika Pesan B tiba sebelum Pesan A?’ atau ‘Apa yang terjadi jika sistem mengalami kegagalan antara langkah 3 dan langkah 4?’ Pertanyaan-pertanyaan ini sering mengungkap celah logika.

Strategi Mitigasi Setelah Dikenali 🛡️

Setelah kondisi persaingan divisualisasikan dan dipahami, Anda dapat menerapkan perubahan struktural. Diagram membantu Anda menentukan perubahan arsitektur mana yang tepat.

- Mekanisme Penguncian: Jika diagram menunjukkan akses bersamaan terhadap sumber daya, perkenalkan objek kunci. Dalam diagram, ini muncul sebagai pesan ke Manajer Kunci sebelum mengakses data.

- Penguncian Optimistik: Alih-alih memblokir, gunakan nomor versi. Diagram harus menunjukkan pemeriksaan nomor versi sebelum operasi penulisan.

- Antrian: Jika masalah disebabkan oleh terlalu banyak permintaan paralel, perkenalkan antrian pesan. Diagram berubah dari pemanggilan langsung ke objek antrian yang menyerialkan pesan-pesan tersebut.

- Kunci Idempotensi: Pastikan setiap permintaan memiliki pengenal unik. Diagram harus menunjukkan ID ini dilewatkan dan diperiksa terhadap catatan yang sudah ada.

Memperbarui diagram setelah menerapkan perbaikan ini sangat penting. Ini berfungsi sebagai dokumentasi bagi pengembang di masa depan. Ini membuktikan bahwa desain telah ditinjau dan risiko telah diminimalkan.

Praktik Terbaik untuk Pemeliharaan Diagram 📝

Diagram adalah dokumen hidup. Jika mereka menjadi usang, nilai mereka sebagai alat debugging akan hilang. Pertahankan relevansinya dengan mengikuti praktik-praktik ini.

- Perbarui saat Perubahan Kode: Jika alur logika berubah, diagram harus berubah juga. Jangan biarkan diagram menyimpang dari kenyataan.

- Kontrol Versi: Simpan diagram bersama dengan kode sumber. Ini memastikan bahwa konteks debugging tersedia ketika pengembang baru bergabung.

- Fokus pada Alur: Jangan diagramkan setiap fungsi. Fokus pada jalur kritis di mana kemungkinan konkurensi terjadi.

- Berkolaborasi: Tinjau diagram bersama rekan kerja. Mata yang segar mungkin menangkap jalur yang Anda lewatkan, seperti pekerjaan latar belakang yang terlupakan.

Dokumentasi harus ringkas. Gunakan notasi standar agar siapa pun di tim dapat memahami diagram tanpa legenda. Konsistensi dalam notasi mengurangi beban kognitif saat melakukan debugging.

Perbandingan: Diagram Urutan vs. Diagram Komunikasi 📋

Meskipun diagram urutan lebih umum, diagram komunikasi memiliki keunggulan khusus untuk debugging kondisi persaingan. Keduanya menggunakan notasi yang serupa tetapi menekankan aspek yang berbeda.

- Diagram Urutan: Menekankan waktu. Mereka menunjukkan timeline vertikal yang ketat. Mereka sangat baik untuk memahami urutan pasti kejadian tetapi bisa menjadi kusut dengan hubungan objek yang kompleks.

- Diagram Komunikasi:Menekankan struktur. Mereka menunjukkan bagaimana objek terhubung. Mereka lebih baik untuk melihat ‘jaringan’ interaksi dan mengidentifikasi pusat bersama.

Untuk kondisi persaingan, pandangan struktural sering lebih mengungkapkan. Diagram urutan mungkin menunjukkan bahwa dua pesan terjadi pada waktu yang sama, tetapi diagram komunikasi menunjukkan bahwa keduanya dikirim ke objek yang sama. Wawasan struktural ini langsung menunjuk ke persaingan sumber daya.

Gunakan kriteria berikut untuk memilih:

- Pilih Diagram Urutan: Ketika urutan waktu yang tepat bersifat kompleks dan linier.

- Pilih Diagram Komunikasi: Ketika hubungan antar objek bersifat kompleks dan tidak linier.

Pikiran Akhir tentang Debugging Logika 🎯

Debugging logika membutuhkan lebih dari sekadar melacak kode. Diperlukan pemahaman terhadap interaksi antar komponen. Diagram komunikasi memberikan pandangan tingkat tinggi terhadap interaksi ini. Dengan memvisualisasikan aliran pesan dan pembagian sumber daya, Anda dapat mengidentifikasi kondisi persaingan sebelum menyebabkan kerusakan data.

Proses ini bersifat iteratif. Gambar diagram, analisis jalur, identifikasi bahaya, lalu perbaiki logika. Siklus ini memastikan sistem tetap kuat di bawah beban konkuren. Hindari godaan untuk hanya mengandalkan uji otomatis, karena mereka sering melewatkan kasus tepi yang bergantung pada waktu. Memvisualisasikan logika mendorong Anda menghadapi model konkurensi secara langsung.

Mengadopsi pendekatan ini membangun pemahaman yang lebih dalam terhadap sistem Anda. Ini mengalihkan fokus dari memperbaiki gejala ke memperbaiki desain dasar. Seiring Anda mendapatkan pengalaman dengan diagram ini, Anda akan menemukan bahwa Anda dapat memprediksi masalah konkurensi potensial sebelum menulis satu baris kode pun. Sikap proaktif ini adalah ciri khas praktik rekayasa yang matang.

Ingat, tujuannya adalah kejelasan. Jika diagramnya membingungkan, kemungkinan besar logikanya bermasalah. Sederhanakan model hingga jalur data menjadi tidak bisa disalahartikan. Dengan diagram yang jelas, kondisi persaingan menjadi masalah yang terlihat dan dapat diselesaikan dengan keyakinan.